# microMIPS64® Architecture for Programmers Volume IV-i: Virtualization Module of the microMIPS64® Architecture

Document Number: MD00849 Revision 1.06 December 10, 2013 Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Tech, LLC, a Wave Computing company ("MIPS") and MIPS' affiliates as applicable. Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS or MIPS' affiliates as applicable or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines. Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS (AND MIPS' AFFILIATES AS APPLICABLE) reserve the right to change the information contained in this document to improve function, design or otherwise.

MIPS and MIPS' affiliates do not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS or an authorized third party, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.

MIPS, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS-3, MIPS-3, MIPS-3, microMIPS-32, microMIPS-30, MIPS-30, MIPS-16, MIPS-16e, MIPS-Based, MIPS-Based, MIPS-VERIFIED, Aptiv logo, microAptiv logo, interAptiv logo, microMIPS logo, MIPS Technologies logo, MIPS-VERIFIED logo, proAptiv logo, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, M14K, 5K, 5Kc, 5Kf, 24K, 24Kc, 24Kf, 24KE, 24KEf, 34K, 34Kc, 34Kf, 74K, 74Kc, 74Kf, 1004K, 1004Kc, 1004Kf, 1074Kf, 1074Kc, 1074Kf, R3000, R4000, R5000, Aptiv, ASMACRO, Atlas, "At the core of the user experience.", BusBridge, Bus Navigator, CLAM, Corextend, CoreFPGA, CoreLV, EC, FPGA View, FS2, FS2 FIRST SILICON SOLUTIONS logo, FS2 NAVIGATOR, HyperDebug, HyperJTAG, IASim, iFlowtrace, interAptiv, JALGO, Logic Navigator, Malta, MDMX, MED, MGB, microAptiv, microMIPS, Navigator, OCI, PDtrace, the Pipeline, proAptiv, Pro Series, SEAD-3, SmartMIPS, SOC-it, and YAMON are trademarks or registered trademarks of MIPS and MIPS' affiliates as applicable in the United States and other countries.

All other trademarks referred to herein are the property of their respective owners.

# **Table of Contents**

| Chapter 1: About This Book                                            | 9  |

|-----------------------------------------------------------------------|----|

| 1.1: Typographical Conventions                                        | 9  |

| 1.1.1: Italic Text                                                    |    |

| 1.1.2: Bold Text                                                      |    |

| 1.1.3: Courier Text                                                   |    |

| 1.2: UNPREDICTABLE and UNDEFINED                                      |    |

| 1.2.1: UNPREDICTABLE                                                  |    |

| 1.2.2: UNDEFINED                                                      |    |

| 1.2.3: UNSTABLE                                                       |    |

| 1.3: Special Symbols in Pseudocode Notation                           |    |

| 1.4: For More Information                                             |    |

| Chapter 2: The Virtualization Module of the microMIPS64® Architecture | ·  |

| 2.1: Base Architecture Requirements                                   |    |

| 2.2: Software Detection of the Module                                 |    |

| 2.3: Compliance and Subsetting                                        |    |

| 2.4: Overview of the Virtualization Module                            |    |

| 2.5: Instruction Bit Encoding                                         | 15 |

| Chapter 3: Overview of Virtualization Support                         | 21 |

| 3.1: Overview                                                         |    |

|                                                                       | _  |

| Chapter 4: The Virtualization Privileged Resource Architecture        |    |

| 4.1: Introduction                                                     |    |

| 4.2: Overview                                                         |    |

| 4.3: Compliance                                                       |    |

| 4.4: Operating Modes                                                  |    |

| 4.4.1: The Onion Model                                                |    |

| 4.4.2: Terminology                                                    |    |

| 4.4.3: Definition of Guest Mode                                       |    |

| 4.4.4: The Guest Context                                              |    |

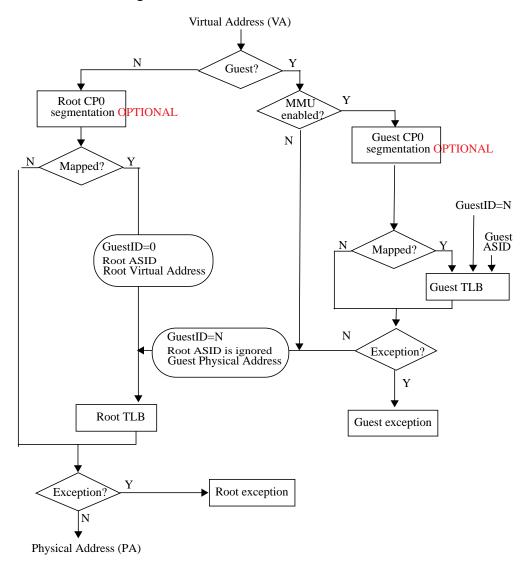

| 4.5: Virtual Memory                                                   |    |

| 4.5.1: Virtualized MMU GuestID Use                                    |    |

| 4.5.2: Root and Guest Shared TLB Operation                            |    |

| 4.5.3: Nested Guest CCA Support                                       |    |

| 4.6: Coprocessor 0                                                    |    |

| 4.6.1: New and Modified CP0 Registers                                 |    |

| 4.6.2: New CP0 Instructions                                           |    |

| 4.6.3: Guest CP0 registers                                            |    |

| 4.6.4: Guest Privileged Sensitive Features                            |    |

| 4.6.5: Access Control for Guest CP0 Register Fields                   |    |

| 4.6.6: Guest Config Register Fields                                   |    |

| 4.6.7: Guest Context Dynamically Set Read-only Fields                 |    |

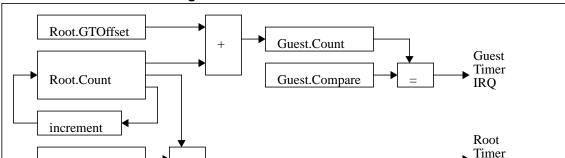

| 4.6.8: Guest Timer                                                    |    |

| 4.6.9: Guest Cache Operations                                         |    |

| 4.6.10: UNPREDICTABLE and UNDEFINED in Guest Mode                     | 56 |

| 4.7: Exceptions                                              |     |

|--------------------------------------------------------------|-----|

| 4.7.1: Exceptions in Guest Mode                              |     |

| 4.7.2: Faulting Address for Exceptions from Guest Mode       |     |

| 4.7.3: Guest initiated Root TLB Exception                    |     |

| 4.7.4: Exception Priority                                    |     |

| 4.7.5: Exception Vector Locations                            |     |

| 4.7.6: Synchronous and Synchronous Hypervisor Exceptions     |     |

| 4.7.7: Guest Privileged Sensitive Instruction Exception      |     |

| 4.7.8: Guest Software Field Change Exception                 |     |

| 4.7.9: Guest Hardware Field Change Exception                 |     |

| 4.7.10: Guest Reserved Instruction Redirect                  |     |

| 4.7.11: Hypercall Exception                                  |     |

| 4.7.12: Guest Exception Code in Root Context                 |     |

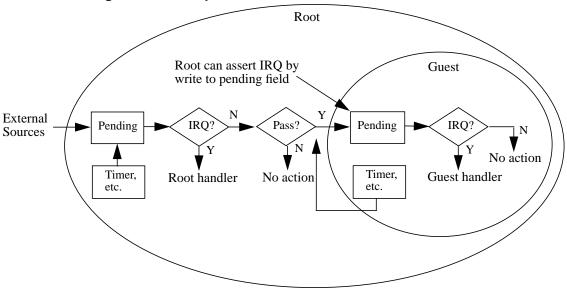

| 4.8: Interrupts                                              |     |

| 4.8.1: External Interrupts                                   |     |

| 4.8.2: Derivation of Guest.CauselP/RIPL                      |     |

| 4.8.3: Timer Interrupts                                      |     |

| 4.8.4: Performance Counter Interrupts                        |     |

| 4.9: Instructions and Machine State, other than CP0          |     |

| 4.9.1: General Purpose Registers and Shadow Register Sets    |     |

| 4.9.2: Multiplier Result Registers                           |     |

| 4.9.3: DSP Module                                            |     |

| 4.9.4: Floating Point Unit (Coprocessor 1)                   |     |

| 4.9.5: Coprocessor 2                                         |     |

| 4.9.6: MSA (MIPS SIMD Architecture)                          |     |

| 4.9.7: User FR Feature                                       |     |

| 4.9.8: LL/SC LLbit Handling                                  |     |

| 4.9.9: XPA: Extended Physical Address                        |     |

| 4.9.10: SDBBP Instruction Handling                           |     |

| 4.10: Combining the Virtualization Module and the MT Module  |     |

| 4.11: Guest Mode and Debug features                          |     |

| 4.12: Watchpoint Debug Support                               |     |

| 4.13: Virtualization Module reatures and Hypervisor Software |     |

| 4.14.1: Introduction                                         |     |

| 4.14.2: Support for Lightweight Virtualization               |     |

| 4.14.2. Support for Lightweight Virtualization               | 91  |

| Chapter 5: Coprocessor 0 (CP0) Registers                     |     |

| 5.1: CP0 Register Summary                                    | 101 |

| 5.2: GuestCtl0 Register (CP0 Register 12, Select 6)          |     |

| 5.3: GuestCtl1 Register (CP0 Register 10, Select 4)          |     |

| 5.4: GuestCtl2 Register (CP0 Register 10, Select 5)          |     |

| 5.5: GuestCtl3 Register (CP0 Register 10, Select 6)          |     |

| 5.6: GuestCtl0Ext Register (CP0 Register 11, Select 4)       |     |

| 5.7: GTOffset Register (CP0 Register 12, Select 7)           |     |

| 5.8: Cause Register (CP0 Register 13, Select 0)              |     |

| 5.9: Configuration Register 3 (CP0 Register 16, Select 3)    |     |

| 5.10: WatchHi Register (CP0 Register 19)                     |     |

| 5.11: Performance Counter Register (CP0 Register 25)         |     |

| 5.12: Note on future CP0 features                            | 124 |

| Chapter 6: Instruction Descriptions                          | 125 |

| 6.1: Overview                                                | 125 |

| App | pendix A: Revision History          | 171 |

|-----|-------------------------------------|-----|

|     | 7.1. Potential areas of improvement | 168 |

|     | 7.1: Potential areas of improvement |     |

| Cha | apter 7: Notes                      | 160 |

|     | ILBWK                               | 166 |

|     | TLBWITLBWR                          |     |

|     | TLBR                                |     |

|     | TLBP                                |     |

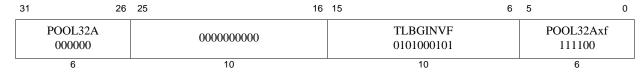

|     | TLBINVF                             |     |

|     | TLBINV                              |     |

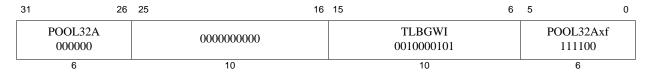

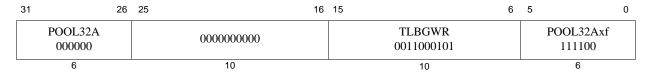

|     | TLBGWR                              |     |

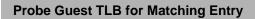

|     | TLBGWI                              |     |

|     | TLBGR                               |     |

|     | TLBGP                               |     |

|     | TLBGINVF                            |     |

|     | TLBGINV                             |     |

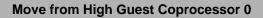

|     | MTHGC0                              | 139 |

|     | MTGC0                               | 137 |

|     | MFHGC0                              |     |

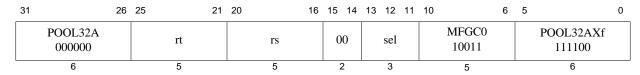

|     | MFGC0                               |     |

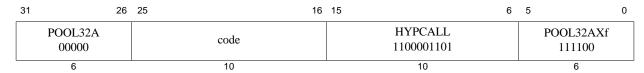

|     | HYPCALL                             |     |

|     | DMTGC0                              | 129 |

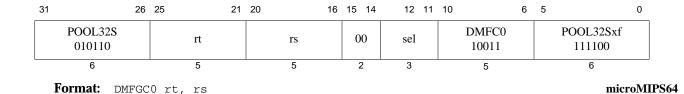

|     | DMFGC0                              | 128 |

# **List of Figures**

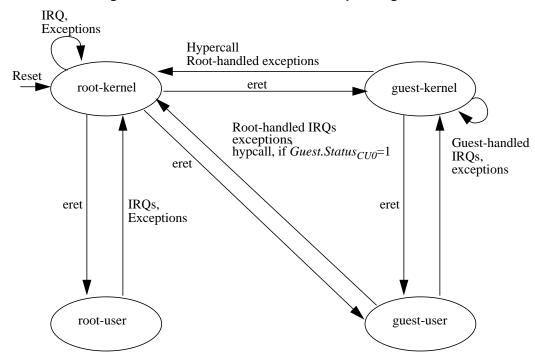

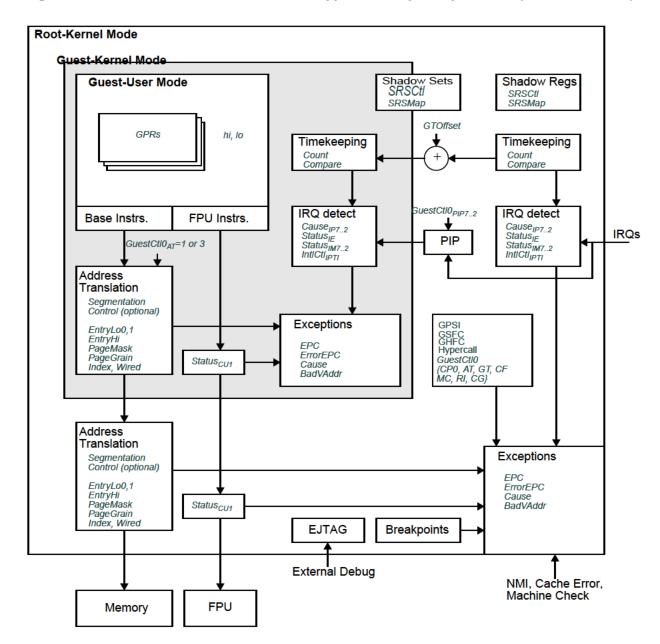

| Figure 4.1: State Transitions between Operating Modes                                               | 25  |

|-----------------------------------------------------------------------------------------------------|-----|

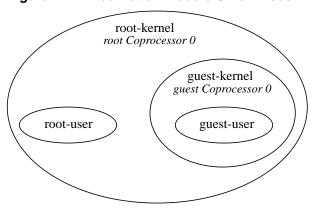

| Figure 4.2: Virtualization Module Onion Model                                                       | 25  |

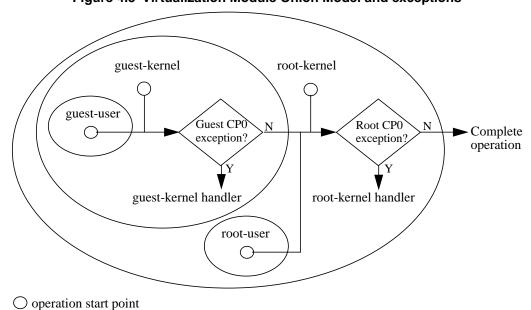

| Figure 4.3: Virtualization Module Onion Model and exceptions                                        | 26  |

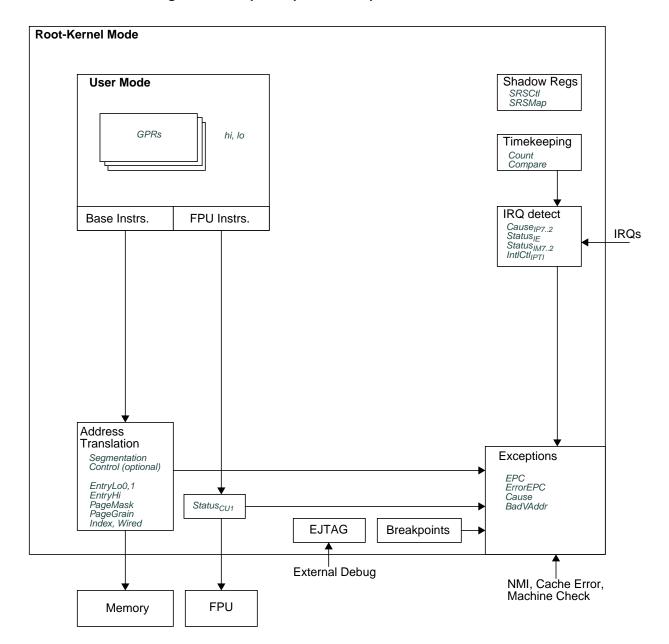

| Figure 4.4: Simplified processor operation in root mode                                             |     |

| Figure 4.5: Virtualization Module Onion Model applied to simplified processor (full virtualization) | 33  |

| Figure 4.6: Outline of Address Translation                                                          |     |

| Figure 4.7: Root and Guest Timers                                                                   | 56  |

| Figure 4.8: Interrupts in the Virtualization Module onion model                                     | 72  |

| Figure 4.9: Guest and Root CauseIP (non-EIC) Virtualization                                         | 75  |

| Figure 4.10: A MT Module processor equipped with three VPEs                                         | 86  |

| Figure 4.11: A MT Module processor equipped with three VPEs and the Virtualization Module           |     |

| Figure 5.1: GuestCtI0 Register Format                                                               | 102 |

| Figure 5.2: GuestCtl1 Register Format                                                               | 111 |

| Figure 5.3: GuestCtl2 Register Format for non-EIC mode                                              |     |

| Figure 5.4: GuestCtl2 Register Format for EIC mode                                                  | 112 |

| Figure 5.5: GuestCtl3 Register Format                                                               | 115 |

| Figure 5.6: GuestCtI0Ext Register Format                                                            | 115 |

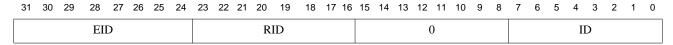

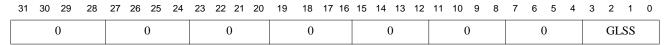

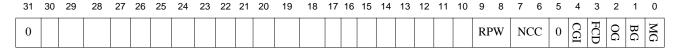

| Figure 5.7: GTOffset Register Format                                                                |     |

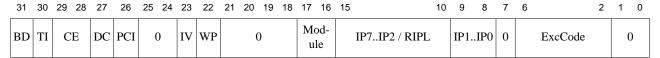

| Figure 5.8: Virtualization Module Cause Register Format                                             | 119 |

| Figure 5-9: Config3 Register Format                                                                 | 120 |

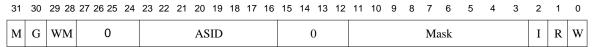

| Figure 5-10: WatchHi Register Format                                                                | 121 |

| Figure 5-11: Performance Counter Control Register Format                                            | 122 |

|                                                                                                     |     |

# **List of Tables**

| Table 1.1: Symbols Used in Instruction Operation Statements                            | 11  |

|----------------------------------------------------------------------------------------|-----|

| Table 2.1: Symbols Used in the Instruction Encoding Tables                             |     |

| Table 2.2: microMIPS64 Encoding of Major Opcode Field in Virtualization Module         | 17  |

| Table 2.3: POOL32A Encoding of Minor Opcode Field in Virtualization Module             | 17  |

| Table 2.4: POOL32Axf Encoding of Minor Opcode Extension Field in Virtualization Module |     |

| Table 2-1: POOL32Axp Encoding of Minor Opcode Extension Field in Virtualization Module | 18  |

| Table 2.5: POOL32S Encoding of Minor Opcode Field                                      |     |

| Table 2.6: POOL32Sxf Encoding of Minor Opcode Extension Field                          |     |

| Table 4.1: Guest, Root and Debug modes                                                 |     |

| Table 4.2: GuestID Translation Related Usage Mode Control                              |     |

| Table 4.3: GuestID Use by TLB instructions.                                            |     |

| Table 4.4: Guest Nested CCA                                                            |     |

| Table 4.5: CP0 Registers Introduced by the Virtualization Module                       |     |

| Table 4.6: CP0 Registers Modified by the Virtualization Module                         |     |

| Table 4.7: CP0 Instructions Introduced by the Virtualization Module                    |     |

| Table 4.8: CP0 Registers in Guest CP0 context                                          |     |

| Table 4.9: Root Modification of Guest CP0 Configuration                                |     |

| Table 4.10: Guest CP0 Fields Subject to Software or Hardware Field Change Exception    |     |

| Table 4.11: Guest CP0 Read-only Config Fields Writable from Root Mode                  |     |

| Table 4.12: Guest CP0 Read-only Fields Writable from Root Mode                         |     |

| Table 4.13: Priority of Exceptions                                                     |     |

| Table 4.14: Exception Type Characteristics                                             |     |

| Table 4.15: Hypervisor Exception Conditions                                            |     |

| Table 4.16: Root effect on Guest XPA control                                           |     |

| Table 4.17: Virtualization control of SDBBP execution                                  |     |

| Table 4.18: Debug Features and Application to Virtualization Module                    |     |

| Table 4.19: Guest Watchpoint Support                                                   |     |

| Table 4.20: Watch Control                                                              |     |

| Table 4.21: Virtualization Optimizations and their Intended Purpose                    |     |

| Table 4.22: MMU Configurations with RPU                                                |     |

| Table 5.1: Virtualization Module Changes to Coprocessor 0 Registers in Numerical Order |     |

| Table 5.2: GuestCtl0 Register Field Descriptions                                       |     |

| Table 5.3: GuestCtl0 GExcCode values                                                   |     |

| Table 5.4: GuestCtl1 Register Field Descriptions                                       |     |

| Table 5.5: non-EIC mode GuestCtl2 Register Field Descriptions                          |     |

| Table 5.6: EIC mode GuestCtl2 Register Field Descriptions                              |     |

| Table 5.7: GuestCtl3 Register Field Descriptions                                       |     |

| Table 5.8: GuestCtl0Ext Register Field Descriptions                                    |     |

| Table 5.9: GTOffset Register Field Descriptions                                        |     |

| Table 5.11: Cause Register ExcCode values                                              |     |

| Table 5.10: Cause Register Field Description, modified by Virtualization Module        |     |

| Table 5.13: WatchHi Register Field Descriptions                                        |     |

| Table 5.12: Config3 Register Field Descriptions                                        |     |

| Table 5.14: New Performance Counter Control Register Field Descriptions                |     |

| Table 6.1: New and Modified Instructions                                               | 125 |

# **About This Book**

The microMIPS64® Architecture for Programmers Volume IV-i: Virtualization Module of the microMIPS64® Architecture comes as part of a multi-volume set.

- Volume I-A describes conventions used throughout the document set, and provides an introduction to the MIPS64® Architecture

- Volume I-B describes conventions used throughout the document set, and provides an introduction to the microMIPS64<sup>TM</sup> Architecture

- Volume II-A provides detailed descriptions of each instruction in the MIPS64® instruction set

- Volume II-B provides detailed descriptions of each instruction in the microMIPS64<sup>TM</sup> instruction set

- Volume III describes the MIPS64® and microMIPS64<sup>TM</sup> Privileged Resource Architecture which defines and governs the behavior of the privileged resources included in a MIPS® processor implementation

- Volume IV-a describes the MIPS16e<sup>TM</sup> Application-Specific Extension to the MIPS64® Architecture. Beginning with Release 3 of the Architecture, microMIPS is the preferred solution for smaller code size.

- Volume IV-b describes the MDMX<sup>TM</sup> Application-Specific Extension to the MIPS64® Architecture and microMIPS64<sup>TM</sup>. With Release 5 of the Architecture, MDMX is deprecated. MDMX and MSA can not be implemented at the same time.

- Volume IV-c describes the MIPS-3D® Application-Specific Extension to the MIPS® Architecture

- Volume IV-d describes the SmartMIPS®Application-Specific Extension to the MIPS32® Architecture and the microMIPS32<sup>TM</sup> Architecture and is not applicable to the MIPS64® document set nor the microMIPS64<sup>TM</sup> document set.

- Volume IV-e describes the MIPS® DSP Module to the MIPS® Architecture

- Volume IV-f describes the MIPS® MT Module to the MIPS® Architecture

- Volume IV-h describes the MIPS® MCU Application-Specific Extension to the MIPS® Architecture

- Volume IV-i describes the MIPS® Virtualization Module to the MIPS® Architecture

- Volume IV-j describes the MIPS® SIMD Architecture Module to the MIPS® Architecture

# 1.1 Typographical Conventions

This section describes the use of *italic*, **bold** and courier fonts in this book.

#### 1.1.1 Italic Text

- is used for emphasis

- is used for *bits*, *fields*, *registers*, that are important from a software perspective (for instance, address bits used by software, and programmable fields and registers), and various *floating point instruction formats*, such as *S*, *D*, and *PS*

- is used for the memory access types, such as cached and uncached

#### 1.1.2 Bold Text

- represents a term that is being defined

- is used for **bits** and **fields** that are important from a hardware perspective (for instance, **register** bits, which are not programmable but accessible only to hardware)

- is used for ranges of numbers; the range is indicated by an ellipsis. For instance, **5..1** indicates numbers 5 through

- is used to emphasize UNPREDICTABLE and UNDEFINED behavior, as defined below.

#### 1.1.3 Courier Text

Courier fixed-width font is used for text that is displayed on the screen, and for examples of code and instruction pseudocode.

#### 1.2 UNPREDICTABLE and UNDEFINED

The terms **UNPREDICTABLE** and **UNDEFINED** are used throughout this book to describe the behavior of the processor in certain cases. **UNDEFINED** behavior or operations can occur only as the result of executing instructions in a privileged mode (i.e., in Kernel Mode or Debug Mode, or with the CPO usable bit set in the Status register). Unprivileged software can never cause **UNDEFINED** behavior or operations. Conversely, both privileged and unprivileged software can cause **UNPREDICTABLE** results or operations.

#### 1.2.1 UNPREDICTABLE

**UNPREDICTABLE** results may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. Software can never depend on results that are **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause a result to be generated or not. If a result is generated, it is **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause arbitrary exceptions.

**UNPREDICTABLE** results or operations have several implementation restrictions:

- Implementations of operations generating **UNPREDICTABLE** results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

- UNPREDICTABLE operations must not read, write, or modify the contents of memory or internal state which

is inaccessible in the current processor mode. For example, UNPREDICTABLE operations executed in user

mode must not access memory or internal state that is only accessible in Kernel Mode or Debug Mode or in

another process

UNPREDICTABLE operations must not halt or hang the processor

#### 1.2.2 UNDEFINED

**UNDEFINED** operations or behavior may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. **UNDEFINED** operations or behavior may vary from nothing to creating an environment in which execution can no longer continue. **UNDEFINED** operations or behavior may cause data loss.

**UNDEFINED** operations or behavior has one implementation restriction:

• **UNDEFINED** operations or behavior must not cause the processor to hang (that is, enter a state from which there is no exit other than powering down the processor). The assertion of any of the reset signals must restore the processor to an operational state

#### 1.2.3 UNSTABLE

**UNSTABLE** results or values may vary as a function of time on the same implementation or instruction. Unlike **UNPREDICTABLE** values, software may depend on the fact that a sampling of an **UNSTABLE** value results in a legal transient value that was correct at some point in time prior to the sampling.

**UNSTABLE** values have one implementation restriction:

• Implementations of operations generating **UNSTABLE** results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

## 1.3 Special Symbols in Pseudocode Notation

In this book, algorithmic descriptions of an operation are described as pseudocode in a high-level language notation resembling Pascal. Special symbols used in the pseudocode notation are listed in Table 1.1.

**Table 1.1 Symbols Used in Instruction Operation Statements**

| Symbol           | Meaning                                                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>←</b>         | Assignment                                                                                                                                                                                                                                                        |

| =, ≠             | Tests for equality and inequality                                                                                                                                                                                                                                 |

|                  | Bit string concatenation                                                                                                                                                                                                                                          |

| x <sup>y</sup>   | A y-bit string formed by y copies of the single-bit value x                                                                                                                                                                                                       |

| b#n              | A constant value $n$ in base $b$ . For instance 10#100 represents the decimal value 100, 2#100 represents the binary value 100 (decimal 4), and 16#100 represents the hexadecimal value 100 (decimal 256). If the "b#" prefix is omitted, the default base is 10. |

| 0bn              | A constant value $n$ in base 2. For instance 0b100 represents the binary value 100 (decimal 4).                                                                                                                                                                   |

| 0xn              | A constant value $n$ in base $16$ . For instance $0x100$ represents the hexadecimal value $100$ (decimal $256$ ).                                                                                                                                                 |

| x <sub>y z</sub> | Selection of bits $y$ through $z$ of bit string $x$ . Little-endian bit notation (rightmost bit is 0) is used. If $y$ is less than $z$ , this expression is an empty (zero length) bit string.                                                                    |

| +, -             | 2's complement or floating point arithmetic: addition, subtraction                                                                                                                                                                                                |

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol        | Meaning                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| *,×           | 2's complement or floating point multiplication (both used for either)                                                                                                                                                                                                                                         |  |  |  |  |  |

| div           | 2's complement integer division                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| mod           | 2's complement modulo                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| /             | Floating point division                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| <             | 2's complement less-than comparison                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| >             | 2's complement greater-than comparison                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| ≤             | 2's complement less-than or equal comparison                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| ≥             | 2's complement greater-than or equal comparison                                                                                                                                                                                                                                                                |  |  |  |  |  |

| nor           | Bitwise logical NOR                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| xor           | Bitwise logical XOR                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| and           | Bitwise logical AND                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| or            | Bitwise logical OR                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| not           | Bitwise inversion                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| &&            | Logical (non-Bitwise) AND                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| <<            | Logical Shift left (shift in zeros at right-hand-side)                                                                                                                                                                                                                                                         |  |  |  |  |  |

| >>            | Logical Shift right (shift in zeros at left-hand-side)                                                                                                                                                                                                                                                         |  |  |  |  |  |

| GPRLEN        | The length in bits (32 or 64) of the CPU general-purpose registers                                                                                                                                                                                                                                             |  |  |  |  |  |

| GPR[x]        | CPU general-purpose register $x$ . The content of $GPR[0]$ is always zero. In Release 2 of the Architecture, $GPR[x]$ is a short-hand notation for $SGPR[SRSCtl_{CSS}, x]$ .                                                                                                                                   |  |  |  |  |  |

| SGPR[s,x]     | In Release 2 of the Architecture and subsequent releases, multiple copies of the CPU general-purpose registers may be implemented. SGPR[s,x] refers to GPR set s, register x.                                                                                                                                  |  |  |  |  |  |

| FPR[x]        | Floating Point operand register x                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| FCC[CC]       | Floating Point condition code CC. FCC[0] has the same value as COC[1].                                                                                                                                                                                                                                         |  |  |  |  |  |

| FPR[x]        | Floating Point (Coprocessor unit 1), general register <i>x</i>                                                                                                                                                                                                                                                 |  |  |  |  |  |

| CPR[z,x,s]    | Coprocessor unit z, general register x, select s                                                                                                                                                                                                                                                               |  |  |  |  |  |

| CP2CPR[x]     | Coprocessor unit 2, general register <i>x</i>                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| CCR[z,x]      | Coprocessor unit z, control register x                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| CP2CCR[x]     | Coprocessor unit 2, control register <i>x</i>                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| COC[z]        | Coprocessor unit z condition signal                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Xlat[x]       | Translation of the MIPS16e GPR number x into the corresponding 32-bit GPR number                                                                                                                                                                                                                               |  |  |  |  |  |

| BigEndianMem  | Endian mode as configured at chip reset (0 $\rightarrow$ Little-Endian, 1 $\rightarrow$ Big-Endian). Specifies the endianness of the memory interface (see LoadMemory and StoreMemory pseudocode function descriptions), and the endianness of Kernel and Supervisor mode execution.                           |  |  |  |  |  |

| BigEndianCPU  | The endianness for load and store instructions ( $0 \rightarrow \text{Little-Endian}$ , $1 \rightarrow \text{Big-Endian}$ ). In User mode, this endianness may be switched by setting the <i>RE</i> bit in the <i>Status</i> register. Thus, BigEndianCPU may be computed as (BigEndianMem XOR ReverseEndian). |  |  |  |  |  |

| ReverseEndian | Signal to reverse the endianness of load and store instructions. This feature is available in User mode only, and is implemented by setting the $RE$ bit of the $Status$ register. Thus, ReverseEndian may be computed as $(SR_{RE} \text{ and User mode})$ .                                                  |  |  |  |  |  |

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol               | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| LLbit                | Bit of <b>virtual</b> state used to specify operation for instructions that provide atomic read-modify-write. <i>LLbit</i> is set when a linked load occurs and is tested by the conditional store. It is cleared, during other CPU operation, when a store to the location would no longer be atomic. In particular, it is cleared by exception return instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| I:,<br>I+n:,<br>I-n: | This occurs as a prefix to <i>Operation</i> description lines and functions as a label. It indicates the instruction time during which the pseudocode appears to "execute." Unless otherwise indicated, all effects of the current instruction appear to occur during the instruction time of the current instruction. No label is equivalent to a time label of <b>I</b> . Sometimes effects of an instruction appear to occur either earlier or later — that is, during the instruction time of another instruction. When this happens, the instruction operation is written in sections labeled with the instruction time, relative to the current instruction <b>I</b> , in which the effect of that pseudocode appears to occur. For example, an instruction may have a result that is not available until after the next instruction. Such an instruction has the portion of the instruction operation description that writes the result register in a section labeled <b>I+1</b> .  The effect of pseudocode statements for the current instruction labelled <b>I+1</b> appears to occur "at the same time" as the effects of the statements labeled <b>I</b> for the following instruction. Within one pseudocode sequence, the effects of the statements take place in order. However, between sequences of statements for different instructions that occur "at the same time," there is no defined order. Programs must not depend on a particular order of evaluation between such sections. |  |  |  |  |  |  |

| PC                   | The <i>Program Counter</i> value. During the instruction time of an instruction, this is the address of the instruction word. The address of the instruction that occurs during the next instruction time is determined by assigning a value to <i>PC</i> during an instruction time. If no value is assigned to <i>PC</i> during an instruction time by any pseudocode statement, it is automatically incremented by either 2 (in the case of a 16-bit MIPS16e instruction) or 4 before the next instruction time. A taken branch assigns the target address to the <i>PC</i> during the instruction time of the instruction in the branch delay slot.  In the MIPS Architecture, the PC value is only visible indirectly, such as when the processor stores the restart address into a GPR on a jump-and-link or branch-and-link instruction, or into a Coprocessor 0 register on an exception. The PC value contains a full 64-bit address all of which are significant during a memory ref-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| ISA Mode             | In processors that implement the MIPS16e Application Specific Extension or the microMIPS base architectures, the <i>ISA Mode</i> is a single-bit register that determines in which mode the processor is executing, as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|                      | Encoding Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                      | 0 The processor is executing 32-bit MIPS instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                      | The processor is executing MIIPS16e or microMIPS instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                      | In the MIPS Architecture, the ISA Mode value is only visible indirectly, such as when the processor stores a combined value of the upper bits of PC and the ISA Mode into a GPR on a jump-and-link or branch-and-link instruction, or into a Coprocessor 0 register on an exception.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| PABITS               | The number of physical address bits implemented is represented by the symbol PABITS. As such, if 36 physical address bits were implemented, the size of the physical address space would be $2^{PABITS} = 2^{36}$ bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| SEGBITS              | The number of virtual address bits implemented in a segment of the address space is represented by the symbol SEGBITS. As such, if 40 virtual address bits are implemented in a segment, the size of the segment is $2^{\text{SEGBITS}} = 2^{40}$ bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol                               | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FP32RegistersMode                    | Indicates whether the FPU has 32-bit or 64-bit floating point registers (FPRs). It is optional if the FPU has 32 64-bit FPRs in which 64-bit data types are stored in any FPR.                                                                                                                                                                                                                                                                                                           |

|                                      | microMIPS64 implementations have a compatibility mode in which the processor references the FPRs as if it were a microMIPS32 implementation. In such a case <b>FP32RegisterMode</b> is computed from the FR bit in the <i>Status</i> register. If this bit is a 0, the processor operates as if it had 32 32-bit FPRs. If this bit is a 1, the processor operates with 32 64-bit FPRs.  The value of <b>FP32RegistersMode</b> is computed from the FR bit in the <i>Status</i> register. |

| InstructionInBranchDe-<br>laySlot    | Indicates whether the instruction at the Program Counter address was executed in the delay slot of a branch or jump. This condition reflects the <i>dynamic</i> state of the instruction, not the <i>static</i> state. That is, the value is false if a branch or jump occurs to an instruction whose PC immediately follows a branch or jump, but which is not executed in the delay slot of a branch or jump.                                                                          |

| SignalException(exception, argument) | Causes an exception to be signaled, using the exception parameter as the type of exception and the argument parameter as an exception-specific argument). Control does not return from this pseudocode function—the exception is signaled at the point of the call.                                                                                                                                                                                                                      |

## 1.4 For More Information

Various MIPS RISC processor manuals and additional information about MIPS products can be found at the MIPS URL: http://www.mips.com

For comments or questions on the MIPS64® Architecture or this document, send Email to support@mips.com.

# The Virtualization Module of the microMIPS64® Architecture

#### 2.1 Base Architecture Requirements

The Virtualization Application-Specific Extension (Module) requires the following base architecture support:

- **The microMIPS64 Architecture**: The Virtualization Module requires a compliant implementation of the microMIPS64 Architecture, Release 5.00 or later.

- A TLB-based MMU is required.

- Coprocessor 0 registers KScratch1 and KScratch2 are required

#### 2.2 Software Detection of the Module

Software can determine if the Virtualization Module is implemented by checking the state of the VZ bit in the *Config3* CP0 register.

# 2.3 Compliance and Subsetting

The Virtualization Module to the microMIPS64 Architecture provides hardware support for software-controlled platform virtualization. A subset of Virtualization Module instructions and registers must be implemented, but certain instructions and machine state are defined to be optional and may be omitted.

#### 2.4 Overview of the Virtualization Module

The Virtualization Module extends the microMIPS64® Architecture with a set of new instructions and machine state, and makes backward-compatible modifications to existing microMIPS64 features. The Virtualization Module is designed to enable full virtualization of operating systems.

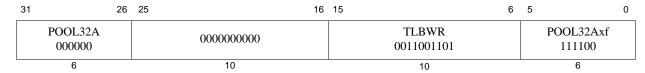

# 2.5 Instruction Bit Encoding

Table 2.2 through Table 2.4 describe the instruction encodings used for the Virtualization Module. Table 2.1 describes the meaning of the symbols used in the tables. These tables only list the instruction encodings for the Virtualization Module instructions. See Volume II-B of this multi-volume set for a full encoding of all instructions.

**Table 2.1 Symbols Used in the Instruction Encoding Tables**

| Symbol | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *      | Operation or field codes marked with this symbol are reserved for future use. Executing such an instruction must cause a Reserved Instruction Exception.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| δ      | (Also <i>italic</i> field name.) Operation or field codes marked with this symbol denotes a field class. The instruction word must be further decoded by examining additional tables that show values for another instruction field.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| β      | Operation or field codes marked with this symbol represent a valid encoding for a higher-order MIPS ISA level. Executing such an instruction must cause a Reserved Instruction Exception.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Т      | Operation or field codes marked with this symbol represent instructions which are not legal if the processor is configured to be backward compatible with MIPS64 processors. If the processor is executing in Kernel Mode, Debug Mode, or 64-bit instructions are enabled, execution proceeds normally. In other cases, executing such an instruction must cause a Reserved Instruction Exception (non-coprocessor encodings or coprocessor instruction encodings for a coprocessor to which access is allowed) or a Coprocessor Unusable Exception (coprocessor instruction encodings for a coprocessor to which access is not allowed).                                                                              |

| θ      | Operation or field codes marked with this symbol are available to licensed MIPS partners. To avoid multiple conflicting instruction definitions, MIPS Technologies will assist the partner in selecting appropriate encodings if requested by the partner. The partner is not required to consult with MIPS Technologies when one of these encodings is used. If no instruction is encoded with this value, executing such an instruction must cause a Reserved Instruction Exception (SPECIAL2 encodings or coprocessor instruction encodings for a coprocessor to which access is allowed) or a Coprocessor Unusable Exception (coprocessor instruction encodings for a coprocessor to which access is not allowed). |

| σ      | Field codes marked with this symbol represent an EJTAG support instruction and implementation of this encoding is optional for each implementation. If the encoding is not implemented, executing such an instruction must cause a Reserved Instruction Exception. If the encoding is implemented, it must match the instruction encoding as shown in the table.                                                                                                                                                                                                                                                                                                                                                       |

| ε      | Operation or field codes marked with this symbol are reserved for MIPS Modules. If the Module is not implemented, executing such an instruction must cause a Reserved Instruction Exception.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ф      | Operation or field codes marked with this symbol are obsolete and will be removed from a future revision of the microMIPS64 ISA. Software should avoid using these operation or field codes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Table 2.2 microMIPS64 Encoding of Major Opcode Field in Virtualization Module

| M | lajor         | MSBMSB-2  |     |           |     |     |     |     |     |       |

|---|---------------|-----------|-----|-----------|-----|-----|-----|-----|-----|-------|

|   |               | 0 1 2     |     | 2         | 3   | 4   | 5   | 6   | 7   | ]     |

|   | SB-3<br>ISB-5 | 000       | 001 | 010       | 011 | 100 | 101 | 110 | 111 |       |

| 0 | 000           | POOL32A δ |     |           |     |     |     |     |     | 1     |

| 1 | 001           |           |     |           |     |     |     |     |     | 16bit |

| 2 | 010           |           |     |           |     |     |     |     |     | 16bit |

| 3 | 011           |           |     |           |     |     |     |     |     | 16bit |

| 4 | 100           |           |     |           |     |     |     |     |     | 1     |

| 5 | 101           |           |     |           |     |     |     |     |     | 1     |

| 6 | 110           |           |     | POOL32S δ |     |     |     |     |     | 1     |

| 7 | 111           |           |     |           |     |     |     |     |     | 1     |

#### Table 2.3 POOL32A Encoding of Minor Opcode Field in Virtualization Module

| M  | inor | bit 53 |     |     |     |     |     |            |             |

|----|------|--------|-----|-----|-----|-----|-----|------------|-------------|

|    |      | 0      | 1   | 2   | 3   | 4   | 5   | 6          | 7           |

| bi | t 20 | 000    | 001 | 010 | 011 | 100 | 101 | 110        | 111         |

| 0  | 000  |        |     |     |     |     |     |            |             |

| 1  | 001  |        |     |     |     |     |     |            |             |

| 2  | 010  |        |     |     |     |     |     |            |             |

| 3  | 011  |        |     |     |     |     |     |            |             |

| 4  | 100  |        |     |     |     |     |     | POOL32Axpδ | POOL32Axf δ |

| 5  | 101  |        |     |     |     |     |     |            |             |

| 6  | 110  |        |     |     |     |     |     |            |             |

| 7  | 111  |        |     |     |     |     |     |            |             |

Table 2.4 POOL32Axf Encoding of Minor Opcode Extension Field in Virtualization Module

| Exte | ension | bit 11. 9 |     |     |     |     |     |     |     |

|------|--------|-----------|-----|-----|-----|-----|-----|-----|-----|

| bi   | t 86   | 0         | 1   | 2   | 3   | 4   | 5   | 6   | 7   |

|      | Ī      | 000       | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

| 0    | 000    |           |     |     |     |     |     |     |     |

| 1    | 001    |           |     |     |     |     |     |     |     |

| 2    | 010    |           |     |     |     |     |     |     |     |

| 3    | 011    |           |     |     |     |     |     |     |     |

| 4    | 100    |           |     |     |     |     |     |     |     |

|   |     | R2 COP0  | R0+ COP0 | R1+ MT COP0 | R1 COP0 | R0+ | R1 | bit1512 |   |

|---|-----|----------|----------|-------------|---------|-----|----|---------|---|

| 5 | 101 | TLBGP    |          |             |         |     |    | 0000    | 0 |

| 5 | 101 | TLBGR    |          |             |         |     |    | 0001    | 1 |

| 5 | 101 | TLBGWI   |          |             |         |     |    | 0010    | 2 |

| 5 | 101 | TLBGWR   |          |             |         |     |    | 0011    | 3 |

| 5 | 101 | TLBGINV  |          |             |         |     |    | 0100    | 4 |

| 5 | 101 | TLBGINVF |          |             |         |     |    | 0101    | 5 |

Table 2.4 POOL32Axf Encoding of Minor Opcode Extension Field (Continued)in Virtualization Module

| 5 | 101 |         |  |  |   |   | 0110 | 6 |

|---|-----|---------|--|--|---|---|------|---|

| 5 | 101 |         |  |  |   |   | 0111 | 7 |

| 5 | 101 |         |  |  |   |   | 1000 | 8 |

| 5 | 101 |         |  |  | * | * | 1001 | 9 |

| 5 | 101 |         |  |  |   |   | 1010 | а |

| 5 | 101 |         |  |  |   |   | 1011 | b |

| 5 | 101 | HYPCALL |  |  |   |   | 1100 | С |

| 5 | 101 |         |  |  |   |   | 1101 | d |

| 5 | 101 |         |  |  |   |   | 1110 | е |

| 5 | 101 |         |  |  |   |   | 1111 | f |

|   |     | R2+ SMART | R1+ SMART |        |       | R2+ MT |       |       |

|---|-----|-----------|-----------|--------|-------|--------|-------|-------|

| 6 | 110 |           |           | MFGC0  | MTGC0 |        | MFGC0 | MTGC0 |

|   |     |           |           |        |       |        |       |       |

|   |     | R2 DSP    | R2 DSP    | R1 DSP |       |        |       |       |

| 7 | 111 |           |           |        |       |        |       |       |

#### Table 2-1POOL32Axp Encoding of Minor Opcode Extension Field in Virtualization Module

| Exte | ension | bit 11. 9 |       |        |        |       |       |        |        |

|------|--------|-----------|-------|--------|--------|-------|-------|--------|--------|

| bi   | t 86   | 0         | 1     | 2      | 3      | 4     | 5     | 6      | 7      |

|      |        | 000       | 001   | 010    | 011    | 100   | 101   | 110    | 111    |

| 0    | 000    |           |       |        |        |       |       |        |        |

| 1    | 001    |           |       |        |        |       |       |        |        |

| 2    | 010    |           |       |        |        |       |       |        |        |

| 3    | 011    | MFHC0     | MTHC0 | MFHGC0 | MTHGC0 | MFHC0 | MTHC0 | MFHGC0 | MTHGC0 |

#### Table 2.5 POOL32S Encoding of Minor Opcode Field

| M  | linor | bit 53 |     |     |     |     |     |     |             |

|----|-------|--------|-----|-----|-----|-----|-----|-----|-------------|

|    |       | 0      | 1   | 2   | 3   | 4   | 5   | 6   | 7           |

| bi | t 20  | 000    | 001 | 010 | 011 | 100 | 101 | 110 | 111         |

| 0  | 000   |        |     |     |     |     |     |     |             |

| 1  | 001   |        |     |     |     |     |     |     |             |

| 2  | 010   |        |     |     |     |     |     |     |             |

| 3  | 011   |        |     |     |     |     |     |     |             |

| 4  | 100   |        |     |     |     |     |     |     | POOL32Sxf δ |

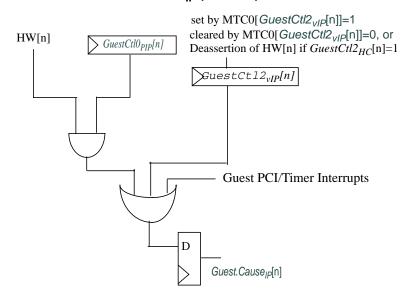

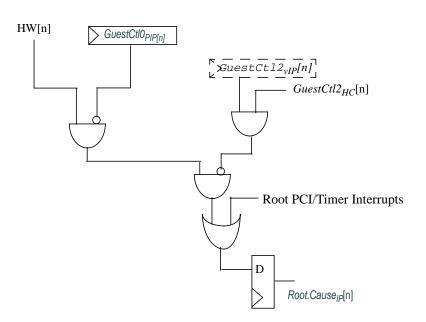

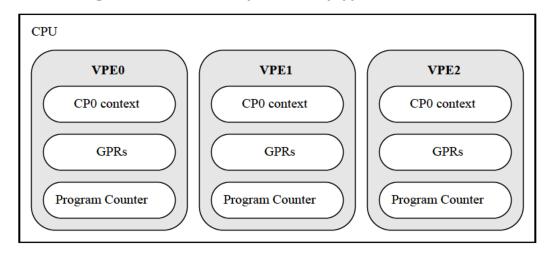

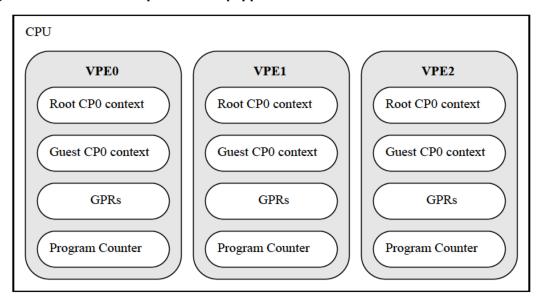

| 5  | 101   |        |     |     |     |     |     |     |             |