# MIPS® Architecture for Programmers Volume IV-h: The MCU Application Specific Extension to the MIPS32® Architecture

Document Number: MD00834 Revision 1.03 September 9, 2013

# **Table of Contents**

| Chapter 1: About This Book                                           | 7  |

|----------------------------------------------------------------------|----|

| 1.1: Typographical Conventions                                       | 7  |

| 1.1.1: Italic Text                                                   | 8  |

| 1.1.2: Bold Text                                                     | 8  |

| 1.1.3: Courier Text                                                  | 8  |

| 1.2: UNPREDICTABLE and UNDEFINED                                     | 8  |

| 1.2.1: UNPREDICTABLE                                                 |    |

| 1.2.2: UNDEFINED                                                     |    |

| 1.2.3: UNSTABLE                                                      |    |

| 1.3: Special Symbols in Pseudocode Notation                          |    |

| 1.4: For More Information                                            |    |

| Chapter 2: Guide to the Instruction Set                              | 13 |

| 2.1: Understanding the Instruction Fields                            |    |

| 2.1.1: Instruction Fields                                            |    |

| 2.1.2: Instruction Descriptive Name and Mnemonic                     |    |

| 2.1.3: Format Field                                                  |    |

| 2.1.4: Purpose Field                                                 |    |

| 2.1.5: Description Field                                             |    |

| 2.1.6: Restrictions Field                                            |    |

| 2.1.7: Operation Field                                               |    |

| 2.1.8: Exceptions Field                                              |    |

| 2.1.9: Programming Notes and Implementation Notes Fields             |    |

| 2.2: Operation Section Notation and Functions                        | 18 |

| 2.2.1: Instruction Execution Ordering                                | 18 |

| 2.2.2: Pseudocode Functions                                          |    |

| 2.2.2.1: Coprocessor General Register Access Functions               | 18 |

| 2.2.2.2: Memory Operation Functions                                  | 20 |

| 2.2.2.3: Floating Point Functions                                    | 23 |

| 2.2.2.4: Miscellaneous Functions                                     | 26 |

| 2.3: Op and Function Subfield Notation                               | 27 |

| 2.4: FPU Instructions                                                | 27 |

| Chapter 3: The MCU Application-Specific Extension to the MIPS32® and |    |

| microMIPS32TMArchitecture                                            | _  |

| 3.1: Base Architecture Requirements                                  |    |

| 3.2: Software Detection of the ASE                                   |    |

| 3.3: Compliance and Subsetting                                       |    |

| 3.4: Overview of the MCU ASE                                         |    |

| 3.4.1: Interrupt Delivery                                            |    |

| 3.4.2: Interrupt Latency Reduction                                   |    |

| 3.4.2.1: Interrupt Vector Prefetching                                |    |

| 3.4.2.2: Automated Interrupt Prologue                                |    |

| 3.4.2.3: Automated Interrupt Epilogue                                |    |

| 3.4.2.4: Interrupt Chaining                                          |    |

| 3.4.3: I/O Device Programming                                        | 30 |

| Chapter 4: The MCU Instruction Set                                   | 31      |

|----------------------------------------------------------------------|---------|

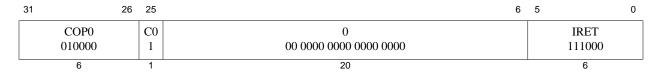

| 4.1: IRET                                                            |         |

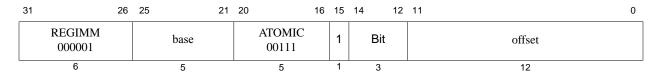

| 4.2: ASET                                                            |         |

| 4.3: ACLR                                                            |         |

|                                                                      |         |

| Chapter 5: The MCU Privileged Resource Architecture                  | 41      |

| 5.1: Introduction                                                    |         |

| 5.2: The MCU System Coprocessor                                      | 41      |

| 5.3: Interrupt Delivery                                              | 41      |

| 5.3.1: Number of Hardware Interrupts                                 | 41      |

| 5.3.1.1: Changes to Vectored Interrupt Mode                          | 41      |

| 5.3.1.2: Changes to External Interrupt Controller Mode               |         |

| 5.4: Interrupt Handling                                              | 42      |

| 5.4.1: Interrupt Vector Prefetching                                  | 42      |

| 5.4.1.1: Historical Behavior of Pipelines with In-Order Completion.  | 42      |

| 5.4.1.2: Historical Behavior of Pipelines with Out-of-Order Complete | tion 42 |

| 5.4.1.3: New Feature - Speculative Prefetching                       | 43      |

| 5.4.2: Interrupt Automated Prologue (IAP)                            | 44      |

| 5.4.2.1: IAP Conditions                                              | 44      |

| 5.4.2.2: IAP Operation                                               | 45      |

| 5.4.2.3: Exceptions during IAP                                       |         |

| 5.4.3: Interrupt Automated Epilogue (IAE)                            |         |

| 5.4.3.1: IAE Conditions                                              | 46      |

| 5.4.3.2: IAE Operation                                               | 46      |

| 5.4.3.3: Exceptions during IAE                                       | 47      |

| 5.4.4: Interrupt Chaining                                            |         |

| 5.4.4.1: Interrupt Chaining Conditions                               |         |

| 5.5: Modified CP0 Registers                                          |         |

| 5.5.1: CP0 Register Summary                                          |         |

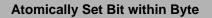

| 5.5.2: Status Register (CP Register 12, Select 0)                    |         |

| 5.5.3: IntCtl (CP0 Registers 12, Select 1)                           |         |

| 5.5.4: View_IPL Register (CP0 Register 12, Select 4)                 |         |

| 5.5.5: SRSMap2 Register (CP0 Register 12, Select 5)                  |         |

| 5.5.6: Cause Register (CP0 Register 13, Select 0)                    |         |

| 5.5.7: View_RIPL Register (CP0 Register 13, Select 4)                |         |

| 5.5.8: Config Register 3 (CP0 Register 16, Select 3)                 | 67      |

| Annondiy A: Povision History                                         | 7:      |

|                                                                      |         |

# **List of Figures**

| Figure 2.1: Example of Instruction Description                      | . 14 |

|---------------------------------------------------------------------|------|

| Figure 2.2: Example of Instruction Fields                           |      |

| Figure 2.3: Example of Instruction Descriptive Name and Mnemonic    |      |

| Figure 2.4: Example of Instruction Format                           |      |

| Figure 2.5: Example of Instruction Purpose                          | . 16 |

| Figure 2.6: Example of Instruction Description                      | . 16 |

| Figure 2.7: Example of Instruction Restrictions                     | . 17 |

| Figure 2.8: Example of Instruction Operation                        |      |

| Figure 2.9: Example of Instruction Exception                        |      |

| Figure 2.10: Example of Instruction Programming Notes               |      |

| Figure 2.11: COP_LW Pseudocode Function                             |      |

| Figure 2.12: COP_LD Pseudocode Function                             |      |

| Figure 2.13: COP_SW Pseudocode Function                             |      |

| Figure 2.14: COP_SD Pseudocode Function                             |      |

| Figure 2.15: CoprocessorOperation Pseudocode Function               |      |

| Figure 2.16: AddressTranslation Pseudocode Function                 |      |

| Figure 2.17: LoadMemory Pseudocode Function                         |      |

| Figure 2.18: StoreMemory Pseudocode Function                        |      |

| Figure 2.19: Prefetch Pseudocode Function                           |      |

| Figure 2.20: SyncOperation Pseudocode Function                      | . 23 |

| Figure 2.21: ValueFPR Pseudocode Function                           |      |

| Figure 2.22: StoreFPR Pseudocode Function                           |      |

| Figure 2.23: CheckFPException Pseudocode Function                   |      |

| Figure 2.24: FPConditionCode Pseudocode Function                    |      |

| Figure 2.25: SetFPConditionCode Pseudocode Function                 |      |

| Figure 2.26: SignalException Pseudocode Function                    |      |

| Figure 2.27: SignalDebugBreakpointException Pseudocode Function     |      |

| Figure 2.28: SignalDebugModeBreakpointException Pseudocode Function |      |

| Figure 2.29: NullifyCurrentInstruction PseudoCode Function          |      |

| Figure 2.30: JumpDelaySlot Pseudocode Function                      |      |

| Figure 2.31: PolyMult Pseudocode Function                           |      |

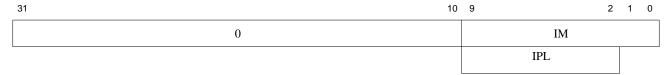

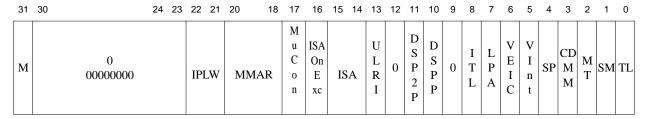

| Figure 5-1: Status Register Format                                  |      |

| Figure 5-2: IntCtl Register Format                                  |      |

| Figure 5-3: View_IPL Register Format                                |      |

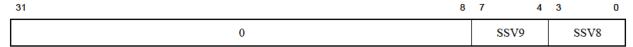

| Figure 5-4: SRSMap Register Format                                  |      |

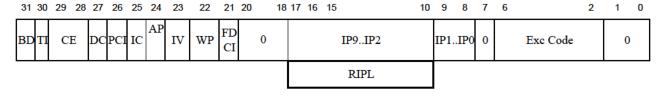

| Figure 5-5: Cause Register Format                                   |      |

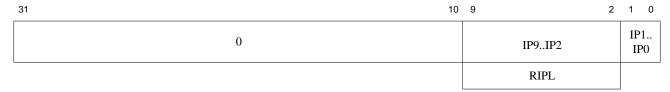

| Figure 5-6: View_RIPL Register Format                               | . 66 |

| Figure 5-7: Config3 Register Format                                 | . 67 |

# **List of Tables**

| Table 1.1: Symbols Used in Instruction Operation Statements                                         | 9  |

|-----------------------------------------------------------------------------------------------------|----|

| Table 2.1: AccessLength Specifications for Loads/Stores                                             |    |

| Table 5.1: Typical Interrupt Handling Flow in Pipelined Implementation with Out-of-Order Completion | 43 |

| Table 5.2: Interrupt Handling Flow with Speculative Prefetching                                     | 44 |

| Table 5.3: MCU Changes to Coprocessor 0 Registers in Numerical Order                                | 48 |

| Table 5.4: Status Register Field Descriptions                                                       | 49 |

| Table 5.5: IntCtl Register Field Descriptions                                                       | 56 |

| Table 5.6: View_IPL Register Field Descriptions                                                     | 60 |

| Table 5.7: SRSMap Register Field Descriptions                                                       | 61 |

| Table 5.8: Cause Register Field Descriptions                                                        | 61 |

| Table 5.9: Cause Register ExcCode Field                                                             | 65 |

| Table 5.10: View_RIPL Register Field Descriptions                                                   | 66 |

| Table 5.11: Config3 Register Field Descriptions                                                     | 67 |

# **About This Book**

The MIPS® Architecture for Programmers Volume IV-h: The MCU Application Specific Extension to the MIPS32® Architecture comes as part of a multi-volume set.

- Volume I-A describes conventions used throughout the document set, and provides an introduction to the MIPS32® Architecture

- Volume I-B describes conventions used throughout the document set, and provides an introduction to the microMIPS32<sup>TM</sup> Architecture

- Volume II-A provides detailed descriptions of each instruction in the MIPS32® instruction set

- Volume II-B provides detailed descriptions of each instruction in the microMIPS32<sup>TM</sup> instruction set

- Volume III describes the MIPS32® and microMIPS32<sup>TM</sup> Privileged Resource Architecture which defines and governs the behavior of the privileged resources included in a MIPS® processor implementation

- Volume IV-a describes the MIPS16e<sup>TM</sup> Application-Specific Extension to the MIPS32® Architecture. Beginning with Release 3 of the Architecture, microMIPS is the preferred solution for smaller code size.

- Volume IV-b describes the MDMX<sup>™</sup> Application-Specific Extension to the MIPS64® Architecture and microMIPS64<sup>™</sup>. It is not applicable to the MIPS32® document set nor the microMIPS32<sup>™</sup> document set. With Release 5 of the Architecture, MDMX is deprecated. MDMX and MSA can not be implemented at the same time.

- Volume IV-c describes the MIPS-3D® Application-Specific Extension to the MIPS® Architecture

- Volume IV-d describes the SmartMIPS®Application-Specific Extension to the MIPS32® Architecture and the microMIPS32™ Architecture .

- Volume IV-e describes the MIPS® DSP Module to the MIPS® Architecture

- Volume IV-f describes the MIPS® MT Module to the MIPS® Architecture

- Volume IV-h describes the MIPS® MCU Application-Specific Extension to the MIPS® Architecture

- Volume IV-i describes the MIPS® Virtualization Module to the MIPS® Architecture

- Volume IV-j describes the MIPS® SIMD Architecture Module to the MIPS® Architecture

# 1.1 Typographical Conventions

This section describes the use of *italic*, **bold** and courier fonts in this book.

#### 1.1.1 Italic Text

- is used for *emphasis*

- is used for *bits*, *fields*, *registers*, that are important from a software perspective (for instance, address bits used by software, and programmable fields and registers), and various *floating point instruction formats*, such as *S*, *D*, and *PS*

- is used for the memory access types, such as cached and uncached

#### 1.1.2 Bold Text

- represents a term that is being defined

- is used for **bits** and **fields** that are important from a hardware perspective (for instance, **register** bits, which are not programmable but accessible only to hardware)

- is used for ranges of numbers; the range is indicated by an ellipsis. For instance, **5..1** indicates numbers 5 through

- is used to emphasize UNPREDICTABLE and UNDEFINED behavior, as defined below.

#### 1.1.3 Courier Text

Courier fixed-width font is used for text that is displayed on the screen, and for examples of code and instruction pseudocode.

#### 1.2 UNPREDICTABLE and UNDEFINED

The terms **UNPREDICTABLE** and **UNDEFINED** are used throughout this book to describe the behavior of the processor in certain cases. **UNDEFINED** behavior or operations can occur only as the result of executing instructions in a privileged mode (i.e., in Kernel Mode or Debug Mode, or with the CPO usable bit set in the Status register). Unprivileged software can never cause **UNDEFINED** behavior or operations. Conversely, both privileged and unprivileged software can cause **UNPREDICTABLE** results or operations.

#### 1.2.1 UNPREDICTABLE

**UNPREDICTABLE** results may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. Software can never depend on results that are **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause a result to be generated or not. If a result is generated, it is **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause arbitrary exceptions.

**UNPREDICTABLE** results or operations have several implementation restrictions:

- Implementations of operations generating UNPREDICTABLE results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

- UNPREDICTABLE operations must not read, write, or modify the contents of memory or internal state which

is inaccessible in the current processor mode. For example, UNPREDICTABLE operations executed in user

mode must not access memory or internal state that is only accessible in Kernel Mode or Debug Mode or in

another process

UNPREDICTABLE operations must not halt or hang the processor

#### 1.2.2 UNDEFINED

**UNDEFINED** operations or behavior may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. **UNDEFINED** operations or behavior may vary from nothing to creating an environment in which execution can no longer continue. **UNDEFINED** operations or behavior may cause data loss.

**UNDEFINED** operations or behavior has one implementation restriction:

• **UNDEFINED** operations or behavior must not cause the processor to hang (that is, enter a state from which there is no exit other than powering down the processor). The assertion of any of the reset signals must restore the processor to an operational state

#### 1.2.3 UNSTABLE

**UNSTABLE** results or values may vary as a function of time on the same implementation or instruction. Unlike **UNPREDICTABLE** values, software may depend on the fact that a sampling of an **UNSTABLE** value results in a legal transient value that was correct at some point in time prior to the sampling.

**UNSTABLE** values have one implementation restriction:

Implementations of operations generating UNSTABLE results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

# 1.3 Special Symbols in Pseudocode Notation

In this book, algorithmic descriptions of an operation are described as pseudocode in a high-level language notation resembling Pascal. Special symbols used in the pseudocode notation are listed in Table 1.1.

Table 1.1 Symbols Used in Instruction Operation Statements

| Symbol           | Meaning                                                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>←</b>         | Assignment                                                                                                                                                                                                                                                        |

| =, ≠             | Tests for equality and inequality                                                                                                                                                                                                                                 |

|                  | Bit string concatenation                                                                                                                                                                                                                                          |

| x <sup>y</sup>   | A <i>y</i> -bit string formed by <i>y</i> copies of the single-bit value <i>x</i>                                                                                                                                                                                 |

| b#n              | A constant value $n$ in base $b$ . For instance 10#100 represents the decimal value 100, 2#100 represents the binary value 100 (decimal 4), and 16#100 represents the hexadecimal value 100 (decimal 256). If the "b#" prefix is omitted, the default base is 10. |

| 0bn              | A constant value $n$ in base 2. For instance 0b100 represents the binary value 100 (decimal 4).                                                                                                                                                                   |

| 0xn              | A constant value $n$ in base $16$ . For instance $0x100$ represents the hexadecimal value $100$ (decimal $256$ ).                                                                                                                                                 |

| x <sub>y z</sub> | Selection of bits <i>y</i> through <i>z</i> of bit string <i>x</i> . Little-endian bit notation (rightmost bit is 0) is used. If <i>y</i> is less than <i>z</i> , this expression is an empty (zero length) bit string.                                           |

| +, -             | 2's complement or floating point arithmetic: addition, subtraction                                                                                                                                                                                                |

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol        | Meaning                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| *,×           | 2's complement or floating point multiplication (both used for either)                                                                                                                                                                                                                                         |  |  |  |  |

| div           | 2's complement integer division                                                                                                                                                                                                                                                                                |  |  |  |  |

| mod           | 2's complement modulo                                                                                                                                                                                                                                                                                          |  |  |  |  |

| /             | Floating point division                                                                                                                                                                                                                                                                                        |  |  |  |  |

| <             | 2's complement less-than comparison                                                                                                                                                                                                                                                                            |  |  |  |  |

| >             | 2's complement greater-than comparison                                                                                                                                                                                                                                                                         |  |  |  |  |

| ≤             | 2's complement less-than or equal comparison                                                                                                                                                                                                                                                                   |  |  |  |  |

| ≥             | 2's complement greater-than or equal comparison                                                                                                                                                                                                                                                                |  |  |  |  |

| nor           | Bitwise logical NOR                                                                                                                                                                                                                                                                                            |  |  |  |  |

| xor           | Bitwise logical XOR                                                                                                                                                                                                                                                                                            |  |  |  |  |

| and           | Bitwise logical AND                                                                                                                                                                                                                                                                                            |  |  |  |  |

| or            | Bitwise logical OR                                                                                                                                                                                                                                                                                             |  |  |  |  |

| not           | Bitwise inversion                                                                                                                                                                                                                                                                                              |  |  |  |  |

| &&            | Logical (non-Bitwise) AND                                                                                                                                                                                                                                                                                      |  |  |  |  |

| <<            | Logical Shift left (shift in zeros at right-hand-side)                                                                                                                                                                                                                                                         |  |  |  |  |

| >>            | Logical Shift right (shift in zeros at left-hand-side)                                                                                                                                                                                                                                                         |  |  |  |  |

| GPRLEN        | The length in bits (32 or 64) of the CPU general-purpose registers                                                                                                                                                                                                                                             |  |  |  |  |

| GPR[x]        | CPU general-purpose register $x$ . The content of $GPR[0]$ is always zero. In Release 2 of the Architecture, $GPR[x]$ is a short-hand notation for $SGPR[SRSCtl_{CSS}, x]$ .                                                                                                                                   |  |  |  |  |

| SGPR[s,x]     | In Release 2 of the Architecture and subsequent releases, multiple copies of the CPU general-purpose regiters may be implemented. <i>SGPR[s,x]</i> refers to GPR set <i>s</i> , register <i>x</i> .                                                                                                            |  |  |  |  |

| FPR[x]        | Floating Point operand register x                                                                                                                                                                                                                                                                              |  |  |  |  |

| FCC[CC]       | Floating Point condition code CC. FCC[0] has the same value as COC[1].                                                                                                                                                                                                                                         |  |  |  |  |

| FPR[x]        | Floating Point (Coprocessor unit 1), general register <i>x</i>                                                                                                                                                                                                                                                 |  |  |  |  |

| CPR[z,x,s]    | Coprocessor unit z, general register x, select s                                                                                                                                                                                                                                                               |  |  |  |  |

| CP2CPR[x]     | Coprocessor unit 2, general register <i>x</i>                                                                                                                                                                                                                                                                  |  |  |  |  |

| CCR[z,x]      | Coprocessor unit z, control register x                                                                                                                                                                                                                                                                         |  |  |  |  |

| CP2CCR[x]     | Coprocessor unit 2, control register <i>x</i>                                                                                                                                                                                                                                                                  |  |  |  |  |

| COC[z]        | Coprocessor unit z condition signal                                                                                                                                                                                                                                                                            |  |  |  |  |

| Xlat[x]       | Translation of the MIPS16e GPR number x into the corresponding 32-bit GPR number                                                                                                                                                                                                                               |  |  |  |  |

| BigEndianMem  | Endian mode as configured at chip reset (0 $\rightarrow$ Little-Endian, 1 $\rightarrow$ Big-Endian). Specifies the endianness of the memory interface (see LoadMemory and StoreMemory pseudocode function descriptions), and the en anness of Kernel and Supervisor mode execution.                            |  |  |  |  |

| BigEndianCPU  | The endianness for load and store instructions ( $0 \rightarrow \text{Little-Endian}$ , $1 \rightarrow \text{Big-Endian}$ ). In User mode, this endianness may be switched by setting the <i>RE</i> bit in the <i>Status</i> register. Thus, BigEndianCPU may be conputed as (BigEndianMem XOR ReverseEndian). |  |  |  |  |

| ReverseEndian | Signal to reverse the endianness of load and store instructions. This feature is available in User mode only and is implemented by setting the <i>RE</i> bit of the <i>Status</i> register. Thus, ReverseEndian may be computed as (SR <sub>RE</sub> and User mode).                                           |  |  |  |  |

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol               | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                           |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| LLbit                | Bit of <b>virtual</b> state used to specify operation for instructions that provide atomic read-modify-write. <i>LLbit</i> is set when a linked load occurs and is tested by the conditional store. It is cleared, during other CPU operation, when a store to the location would no longer be atomic. In particular, it is cleared by exception return instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                           |  |

| I:,<br>I+n:,<br>I-n: | This occurs as a prefix to <i>Operation</i> description lines and functions as a label. It indicates the instruction time during which the pseudocode appears to "execute." Unless otherwise indicated, all effects of the current instruction appear to occur during the instruction time of the current instruction. No label is equivalent to a time label of <b>I</b> . Sometimes effects of an instruction appear to occur either earlier or later — that is, during the instruction time of another instruction. When this happens, the instruction operation is written in sections labeled with the instruction time, relative to the current instruction <b>I</b> , in which the effect of that pseudocode appears to occur. For example, an instruction may have a result that is not available until after the next instruction. Such an instruction has the portion of the instruction operation description that writes the result register in a section labeled <b>I+1</b> .  The effect of pseudocode statements for the current instruction labelled <b>I+1</b> appears to occur "at the same time" as the effect of pseudocode statements labeled <b>I</b> for the following instruction. Within one pseudocode sequence, the effects of the statements take place in order. However, between sequences of statements for different instructions that occur "at the same time," there is no defined order. Programs must not depend on a particular order of evaluation between such sections. |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                           |  |

| PC                   | tion word. The addring a value to <i>PC</i> do pseudocode statemention) or 4 before the instruction time of the In the MIPS Archite address into a GPR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ress of the instruction an instruction, it is autometed next instruction the instruction at the properties of a jump-and | ring the instruction time of an instruction, this is the addruction that occurs during the next instruction time is defection time. If no value is assigned to <i>PC</i> during an instruction time. If no value is assigned to <i>PC</i> during an instruction time. A taken branch assigns the target address to the in the branch delay slot.  value is only visible indirectly, such as when the process delink or branch-and-link instruction, or into a Coprocess a full 32-bit address all of which are significant during | etermined by assign-<br>ruction time by any<br>t MIPS 16e instruc-<br>ne PC during the<br>sor stores the restart<br>ssor 0 register on an |  |

| ISA Mode             | In processors that implement the MIPS16e Application Specific Extension or the microMIPS base architectures, the <i>ISA Mode</i> is a single-bit register that determines in which mode the processor is executing, as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                           |  |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Encoding                                                                                                                 | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                           |  |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                        | The processor is executing 32-bit MIPS instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                           |  |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                        | The processor is executing MIIPS16e or microMIPS instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                           |  |

|                      | In the MIPS Architecture, the ISA Mode value is only visible indirectly, such as when the processor st combined value of the upper bits of PC and the ISA Mode into a GPR on a jump-and-link or branch-an instruction, or into a Coprocessor 0 register on an exception.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                           |  |

| PABITS               | The number of physical address bits implemented is represented by the symbol PABITS. As such, if 36 physical address bits were implemented, the size of the physical address space would be $2^{PABITS} = 2^{36}$ bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                           |  |

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol                               | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FP32RegistersMode                    | Indicates whether the FPU has 32-bit or 64-bit floating point registers (FPRs). In MIPS32 Release 1, the FPU has 32 32-bit FPRs in which 64-bit data types are stored in even-odd pairs of FPRs. In MIPS64, (and optionally in MIPS32 Release2 and MIPSr3) the FPU has 32 64-bit FPRs in which 64-bit data types are stored in any FPR.                                                                                                                                                                                                                    |

|                                      | In MIPS32 Release 1 implementations, <b>FP32RegistersMode</b> is always a 0. MIPS64 implementations have a compatibility mode in which the processor references the FPRs as if it were a MIPS32 implementation. In such a case <b>FP32RegisterMode</b> is computed from the FR bit in the <i>Status</i> register. If this bit is a 0, the processor operates as if it had 32 32-bit FPRs. If this bit is a 1, the processor operates with 32 64-bit FPRs. The value of <b>FP32RegistersMode</b> is computed from the FR bit in the <i>Status</i> register. |

| InstructionInBranchDe-<br>laySlot    | Indicates whether the instruction at the Program Counter address was executed in the delay slot of a branch or jump. This condition reflects the <i>dynamic</i> state of the instruction, not the <i>static</i> state. That is, the value is false if a branch or jump occurs to an instruction whose PC immediately follows a branch or jump, but which is not executed in the delay slot of a branch or jump.                                                                                                                                            |

| SignalException(exception, argument) | Causes an exception to be signaled, using the exception parameter as the type of exception and the argument parameter as an exception-specific argument). Control does not return from this pseudocode function—the exception is signaled at the point of the call.                                                                                                                                                                                                                                                                                        |

# 1.4 For More Information

Various MIPS RISC processor manuals and additional information about MIPS products can be found at the MIPS URL: http://www.mips.com

For comments or questions on the MIPS32® Architecture or this document, send Email to support@mips.com.

# **Guide to the Instruction Set**

This chapter provides a detailed guide to understanding the instruction descriptions, which are listed in alphabetical order in the tables at the beginning of the next chapter.

# 2.1 Understanding the Instruction Fields

Figure 2.1 shows an example instruction. Following the figure are descriptions of the fields listed below:

- "Instruction Fields" on page 14

- "Instruction Descriptive Name and Mnemonic" on page 15

- "Format Field" on page 15

- "Purpose Field" on page 16

- "Description Field" on page 16

- "Restrictions Field" on page 16

- "Operation Field" on page 17

- "Exceptions Field" on page 17

- "Programming Notes and Implementation Notes Fields" on page 18

Instruction Mnemonic and **EXAMPLE Example Instruction Name** Descriptive Name **EXAMPLE** 31 26 25 21 20 16 15 11 10 6 5 0 Instruction encoding constant and variable field **SPECIAL** 0 **EXAMPLE** 0 names and values rt rd 000000 00000 000000 6 5 5 5 5 6 Architecture level at which instruction was defined/redefined Format: MIPS32 EXAMPLE fd, rs, rt Assembler format(s) for each definition **Purpose:** Example Instruction Name Short description -To execute an EXAMPLE op. Symbolic description . **Description:** GPR[rd] ← GPR[r]s exampleop GPR[rt] This section describes the operation of the instruction in text, tables, and illustrations. It Full description of . includes information that would be difficult to encode in the Operation section. instruction operation Restrictions: Restrictions on instruction and operands This section lists any restrictions for the instruction. This can include values of the instruction encoding fields such as register specifiers, operand values, operand formats, address alignment, instruction scheduling hazards, and type of memory access for addressed locations. High-level language Operation: description of instruction operation /\* This section describes the operation of an instruction in \*/ /\* a high-level pseudo-language. It is precise in ways that /\* the Description section is not, but is also missing \* / information that is hard to express in pseudocode. \* / ← GPR[rs] exampleop GPR[rt]  $GPR[rd] \leftarrow temp$ Exceptions that -**Exceptions:** instruction can cause A list of exceptions taken by the instruction Notes for programmers \_ Programming Notes: Information useful to programmers, but not necessary to describe the operation of the instruction Notes for implementors -Implementation Notes:

Figure 2.1 Example of Instruction Description

#### 2.1.1 Instruction Fields

14 MIPS® Architecture for Programmers Volume IV-h: The MCU Application Specific Extension to the MIPS32® Architecture, Revision 1.03

Like *Programming Notes*, except for processor implementors

Fields encoding the instruction word are shown in register form at the top of the instruction description. The following rules are followed:

- The values of constant fields and the *opcode* names are listed in uppercase (SPECIAL and ADD in Figure 2.2). Constant values in a field are shown in binary below the symbolic or hexadecimal value.

- All variable fields are listed with the lowercase names used in the instruction description (rs, rt, and rd in Figure 2.2).

- Fields that contain zeros but are not named are unused fields that are required to be zero (bits 10:6 in Figure 2.2). If such fields are set to non-zero values, the operation of the processor is **UNPREDICTABLE**.

Figure 2.2 Example of Instruction Fields

| 31 26             | 25 21 | 20 16 | 15 11 | 10 6    | 5 0           |

|-------------------|-------|-------|-------|---------|---------------|

| SPECIAL<br>000000 | rs    | rt    | rd    | 0 00000 | ADD<br>100000 |

| 6                 | 5     | 5     | 5     | 5       | 6             |

#### 2.1.2 Instruction Descriptive Name and Mnemonic

The instruction descriptive name and mnemonic are printed as page headings for each instruction, as shown in Figure 2.3.

Figure 2.3 Example of Instruction Descriptive Name and Mnemonic

Add Word ADD

#### 2.1.3 Format Field

The assembler formats for the instruction and the architecture level at which the instruction was originally defined are given in the *Format* field. If the instruction definition was later extended, the architecture levels at which it was extended and the assembler formats for the extended definition are shown in their order of extension (for an example, see C.cond fmt). The MIPS architecture levels are inclusive; higher architecture levels include all instructions in previous levels. Extensions to instructions are backwards compatible. The original assembler formats are valid for the extended architecture.

Figure 2.4 Example of Instruction Format

Format: ADD fd,rs,rt MIPS32

The assembler format is shown with literal parts of the assembler instruction printed in uppercase characters. The variable parts, the operands, are shown as the lowercase names of the appropriate fields. The architectural level at which the instruction was first defined, for example "MIPS32" is shown at the right side of the page.

There can be more than one assembler format for each architecture level. Floating point operations on formatted data show an assembly format with the actual assembler mnemonic for each valid value of the *fmt* field. For example, the ADD fmt instruction lists both ADD.S and ADD.D.

The assembler format lines sometimes include parenthetical comments to help explain variations in the formats (once again, see C.cond.fmt). These comments are not a part of the assembler format.

#### 2.1.4 Purpose Field

The *Purpose* field gives a short description of the use of the instruction.

#### Figure 2.5 Example of Instruction Purpose

Purpose: Add Word

To add 32-bit integers. If an overflow occurs, then trap.

#### 2.1.5 Description Field

If a one-line symbolic description of the instruction is feasible, it appears immediately to the right of the *Description* heading. The main purpose is to show how fields in the instruction are used in the arithmetic or logical operation.

#### Figure 2.6 Example of Instruction Description

**Description:** GPR[rd] ← GPR[rs] + GPR[rt]

The 32-bit word value in GPR *rt* is added to the 32-bit value in GPR *rs* to produce a 32-bit result.

- If the addition results in 32-bit 2's complement arithmetic overflow, the destination register is not modified and an Integer Overflow exception occurs.

- If the addition does not overflow, the 32-bit result is placed into GPR rd.

The body of the section is a description of the operation of the instruction in text, tables, and figures. This description complements the high-level language description in the *Operation* section.

This section uses acronyms for register descriptions. "GPR rt" is CPU general-purpose register specified by the instruction field rt. "FPR fs" is the floating point operand register specified by the instruction field fs. "CP1 register fd" is the coprocessor 1 general register specified by the instruction field fd. "FCSR" is the floating point Control / Status register.

#### 2.1.6 Restrictions Field

The *Restrictions* field documents any possible restrictions that may affect the instruction. Most restrictions fall into one of the following six categories:

- Valid values for instruction fields (for example, see floating point ADD fmt)

- ALIGNMENT requirements for memory addresses (for example, see LW)

- Valid values of operands (for example, see ALNV.PS)

- Valid operand formats (for example, see floating point ADD fmt)

- Order of instructions necessary to guarantee correct execution. These ordering constraints avoid pipeline hazards for which some processors do not have hardware interlocks (for example, see MUL).

- Valid memory access types (for example, see LL/SC)

#### Figure 2.7 Example of Instruction Restrictions

#### **Restrictions:**

None

#### 2.1.7 Operation Field

The *Operation* field describes the operation of the instruction as pseudocode in a high-level language notation resembling Pascal. This formal description complements the *Description* section; it is not complete in itself because many of the restrictions are either difficult to include in the pseudocode or are omitted for legibility.

#### Figure 2.8 Example of Instruction Operation

## Operation:

```

\begin{array}{l} \mathsf{temp} \leftarrow (\mathsf{GPR}[\mathsf{rs}]_{31} \big| \big| \mathsf{GPR}[\mathsf{rs}]_{31..0}) \; + \; (\mathsf{GPR}[\mathsf{rt}]_{31} \big| \big| \mathsf{GPR}[\mathsf{rt}]_{31..0}) \\ \mathsf{if} \; \mathsf{temp}_{32} \neq \mathsf{temp}_{31} \; \mathsf{then} \\ \qquad \qquad \mathsf{SignalException}(\mathsf{IntegerOverflow}) \\ \mathsf{else} \\ \qquad \mathsf{GPR}[\mathsf{rd}] \; \leftarrow \; \mathsf{temp} \\ \mathsf{endif} \end{array}

```

See 2.2 "Operation Section Notation and Functions" on page 18 for more information on the formal notation used here.

#### 2.1.8 Exceptions Field

The *Exceptions* field lists the exceptions that can be caused by *Operation* of the instruction. It omits exceptions that can be caused by the instruction fetch, for instance, TLB Refill, and also omits exceptions that can be caused by asynchronous external events such as an Interrupt. Although a Bus Error exception may be caused by the operation of a load or store instruction, this section does not list Bus Error for load and store instructions because the relationship between load and store instructions and external error indications, like Bus Error, are dependent upon the implementation.

Figure 2.9 Example of Instruction Exception

#### **Exceptions:**

Integer Overflow

An instruction may cause implementation-dependent exceptions that are not present in the *Exceptions* section.

#### 2.1.9 Programming Notes and Implementation Notes Fields

The *Notes* sections contain material that is useful for programmers and implementors, respectively, but that is not necessary to describe the instruction and does not belong in the description sections.

#### Figure 2.10 Example of Instruction Programming Notes

#### **Programming Notes:**

ADDU performs the same arithmetic operation but does not trap on overflow.

# 2.2 Operation Section Notation and Functions

In an instruction description, the *Operation* section uses a high-level language notation to describe the operation performed by each instruction. Special symbols used in the pseudocode are described in the previous chapter. Specific pseudocode functions are described below.

This section presents information about the following topics:

- "Instruction Execution Ordering" on page 18

- "Pseudocode Functions" on page 18

#### 2.2.1 Instruction Execution Ordering

Each of the high-level language statements in the *Operations* section are executed sequentially (except as constrained by conditional and loop constructs).

#### 2.2.2 Pseudocode Functions

There are several functions used in the pseudocode descriptions. These are used either to make the pseudocode more readable, to abstract implementation-specific behavior, or both. These functions are defined in this section, and include the following:

- "Coprocessor General Register Access Functions" on page 18

- "Memory Operation Functions" on page 20

- "Floating Point Functions" on page 23

- "Miscellaneous Functions" on page 26

#### 2.2.2.1 Coprocessor General Register Access Functions

Defined coprocessors, except for CP0, have instructions to exchange words and doublewords between coprocessor general registers and the rest of the system. What a coprocessor does with a word or doubleword supplied to it and how a coprocessor supplies a word or doubleword is defined by the coprocessor itself. This behavior is abstracted into the functions described in this section.

#### COP LW

The COP\_LW function defines the action taken by coprocessor z when supplied with a word from memory during a load word operation. The action is coprocessor-specific. The typical action would be to store the contents of memword in coprocessor general register *rt*.

#### Figure 2.11 COP\_LW Pseudocode Function

```

COP_LW (z, rt, memword)

z: The coprocessor unit number

rt: Coprocessor general register specifier

memword: A 32-bit word value supplied to the coprocessor

/* Coprocessor-dependent action */

endfunction COP_LW

```

#### COP LD

The COP\_LD function defines the action taken by coprocessor z when supplied with a doubleword from memory during a load doubleword operation. The action is coprocessor-specific. The typical action would be to store the contents of memdouble in coprocessor general register *rt*.

#### Figure 2.12 COP\_LD Pseudocode Function

```

COP_LD (z, rt, memdouble)

z: The coprocessor unit number

rt: Coprocessor general register specifier

memdouble: 64-bit doubleword value supplied to the coprocessor.

/* Coprocessor-dependent action */

endfunction COP_LD

```

#### COP SW

The COP\_SW function defines the action taken by coprocessor *z* to supply a word of data during a store word operation. The action is coprocessor-specific. The typical action would be to supply the contents of the low-order word in coprocessor general register *rt*.

#### Figure 2.13 COP\_SW Pseudocode Function

```

dataword ← COP_SW (z, rt)

z: The coprocessor unit number

rt: Coprocessor general register specifier

dataword: 32-bit word value

/* Coprocessor-dependent action */

endfunction COP_SW

```

#### COP SD

The COP\_SD function defines the action taken by coprocessor *z* to supply a doubleword of data during a store doubleword operation. The action is coprocessor-specific. The typical action would be to supply the contents of the low-order doubleword in coprocessor general register *rt*.

#### Figure 2.14 COP\_SD Pseudocode Function

```

datadouble ← COP_SD (z, rt)

z: The coprocessor unit number

rt: Coprocessor general register specifier

datadouble: 64-bit doubleword value

/* Coprocessor-dependent action */

endfunction COP_SD

```

#### **CoprocessorOperation**

The CoprocessorOperation function performs the specified Coprocessor operation.

#### Figure 2.15 CoprocessorOperation Pseudocode Function

```

CoprocessorOperation (z, cop_fun)

/* z: Coprocessor unit number */

/* cop_fun: Coprocessor function from function field of instruction */

/* Transmit the cop_fun value to coprocessor z */

endfunction CoprocessorOperation

```

#### 2.2.2.2 Memory Operation Functions

Regardless of byte ordering (big- or little-endian), the address of a halfword, word, or doubleword is the smallest byte address of the bytes that form the object. For big-endian ordering this is the most-significant byte; for a little-endian ordering this is the least-significant byte.

In the *Operation* pseudocode for load and store operations, the following functions summarize the handling of virtual addresses and the access of physical memory. The size of the data item to be loaded or stored is passed in the *AccessLength* field. The valid constant names and values are shown in Table 2.1. The bytes within the addressed unit of memory (word for 32-bit processors or doubleword for 64-bit processors) that are used can be determined directly from the *AccessLength* and the two or three low-order bits of the address.

#### **AddressTranslation**

The AddressTranslation function translates a virtual address to a physical address and its cacheability and coherency attribute, describing the mechanism used to resolve the memory reference.

Given the virtual address *vAddr*, and whether the reference is to Instructions or Data (*IorD*), find the corresponding physical address (*pAddr*) and the cacheability and coherency attribute (*CCA*) used to resolve the reference. If the virtual address is in one of the unmapped address spaces, the physical address and *CCA* are determined directly by the virtual address. If the virtual address is in one of the mapped address spaces then the TLB or fixed mapping MMU determines the physical address and access type; if the required translation is not present in the TLB or the desired access is not permitted, the function fails and an exception is taken.

#### Figure 2.16 AddressTranslation Pseudocode Function

```

(pAddr, CCA) ← AddressTranslation (vAddr, IorD, LorS)

/* pAddr: physical address */

/* CCA: Cacheability&Coherency Attribute, the method used to access caches*/

```

```

/* and memory and resolve the reference */

/* vAddr: virtual address */

/* IorD: Indicates whether access is for INSTRUCTION or DATA */

/* LorS: Indicates whether access is for LOAD or STORE */

/* See the address translation description for the appropriate MMU */